Accelergy: An Architecture-Level Energy Estimation Methodology for Accelerator Designs

-

Yannan Nellie Wu

MIT -

Joel S. Emer

MIT, NVIDIA -

Vivienne Sze

MIT

Email: accelergy at mit dot edu

Recent News

Sparseloop paper released on arXiv [paper]

Upcoming tutorial at ISCA2021 (virtual) on sparse tensor accelerator abstraction and modeling, June 19th, 2021 [ Register ]

Papers on sparse modeling and hetergeneous computing system modeling presented at ISPASS2021

Abstract

With Moore's law slowing down and Dennard scaling ended, energy-efficient domain-specific accelerators, such as deep neural network (DNN) processors for machine learning and programmable network switches for cloud applications, have become a promising way for hardware designers to continue bringing energy efficiency improvements to data and computation-intensive applications. To ensure the fast exploration of the accelerator design space, architecture-level energy estimators, which perform energy estimations without requiring complete hardware description of the designs, are critical to designers. However, it is difficult to use existing architecture-level energy estimators to obtain accurate estimates for accelerator designs, as accelerator designs are diverse and sensitive to data patterns. This paper presents Accelergy, a generally applicable energy estimation methodology for accelerators that allows design specifications comprised of user-defined high-level compound components and user-defined low-level primitive components, which can be characterized by third-party energy estimation plug-ins.

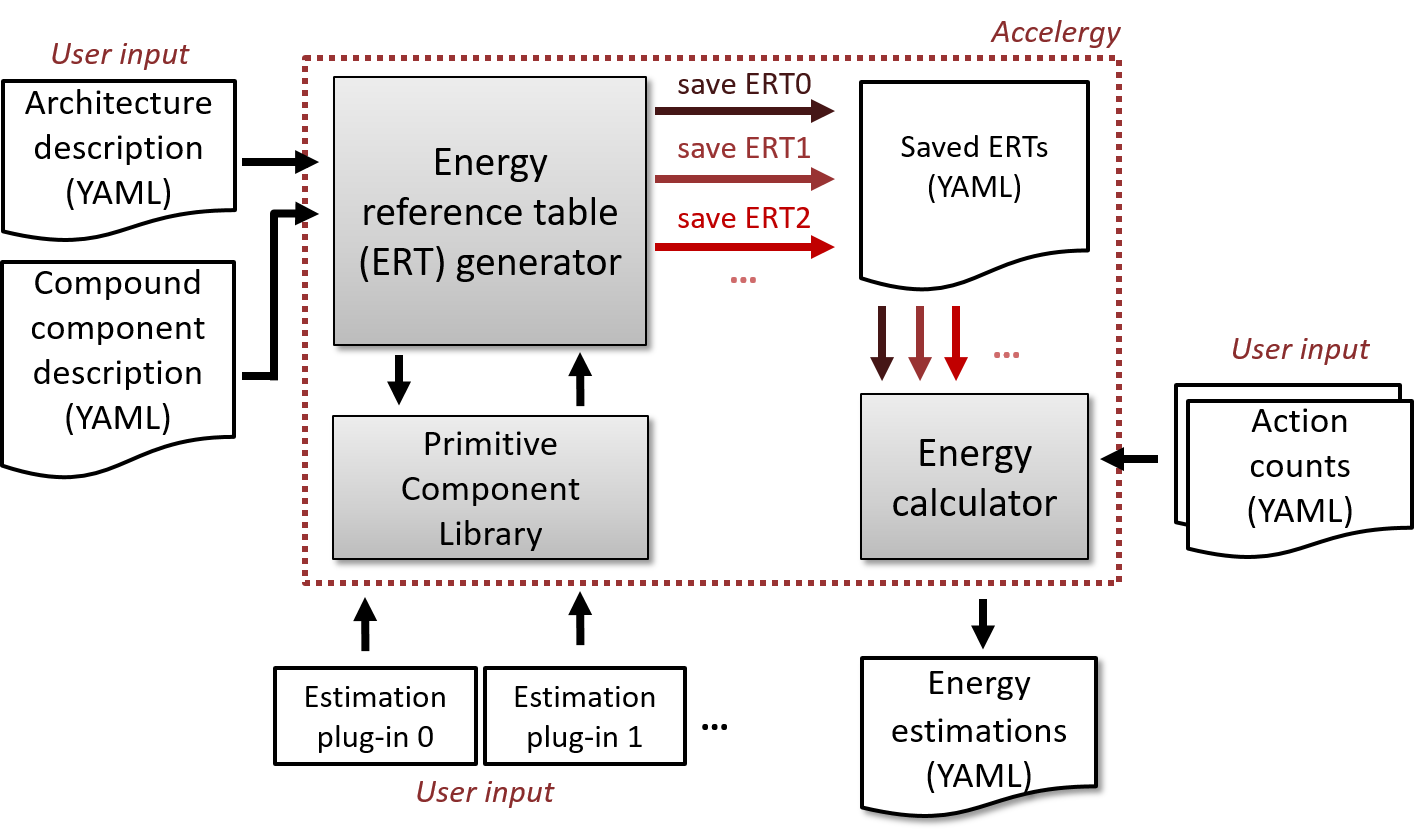

High-level block diagram of Accelergy Framework

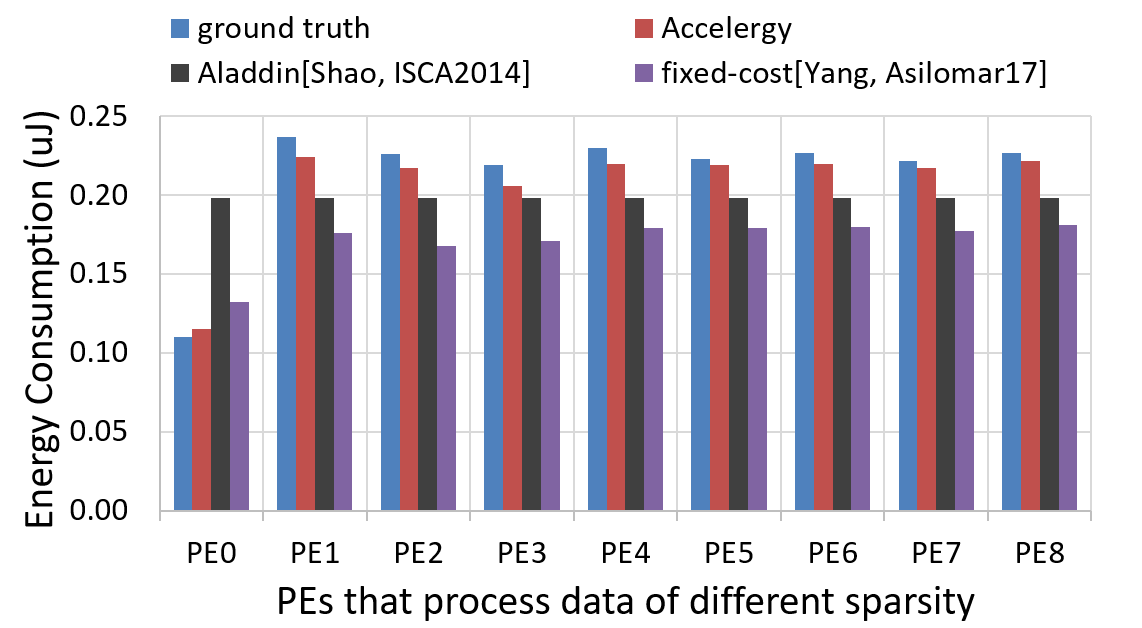

Energy breakdown estimation of Eyeriss

Downloads

Open Source Code

Related Websites

BibTeX

@inproceedings{iccad_2019_accelergy,

author = {Wu, Yannan N. and Emer, Joel S. and Sze, Vivienne},

title = {{Accelergy: An Architecture-Level Energy Estimation Methodology for Accelerator Designs}},

booktitle = {{IEEE/ACM International Conference On Computer Aided Design (ICCAD)}},

year = {{2019}}

}

Related Papers

Y. N. Wu, P.-A. Tsai, A. Parashar, V. Sze, J. S. Emer, “Sparseloop: An Analytical Approach to Sparse Tensor Accelerator Modeling” arXiv, 2022 [ paper ]Y. N. Wu, P.-A. Tsai, A. Parashar, V. Sze, J. S. Emer, “Sparseloop: An Analytical, Energy-Focused Design Space Exploration Methodology for Sparse Tensor Accelerators,” IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), March 2021 [ paper ]

F. Wang, Y. N. Wu, M. Woicik, J. S. Emer, V. Sze, “Architecture-Level Energy Estimation for Heterogeneous Computing Systems,” IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), March 2021 [ paper ]

V. Sze, Y.-H. Chen, T.-J. Yang, J. S. Emer, Efficient Processing of Deep Neural Networks, Synthesis Lectures on Computer Architecture, Morgan & Claypool Publishers, 2020. [ Pre-order book here ] [ Flyer ]

Y. N. Wu, V. Sze, J. S. Emer, “An Architecture-Level Energy and Area Estimator for Processing-In-Memory Accelerator Designs,” IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), April 2020 [ paper ]

Y. N. Wu, J. S. Emer, V. Sze, “Accelergy: An Architecture-Level Energy Estimation Methodology for Accelerator Designs,” International Conference on Computer Aided Design (ICCAD), November 2019 [ paper ] [ slides ]